♦ mm-Wave and THz packing techniques for heterogeneous system integration

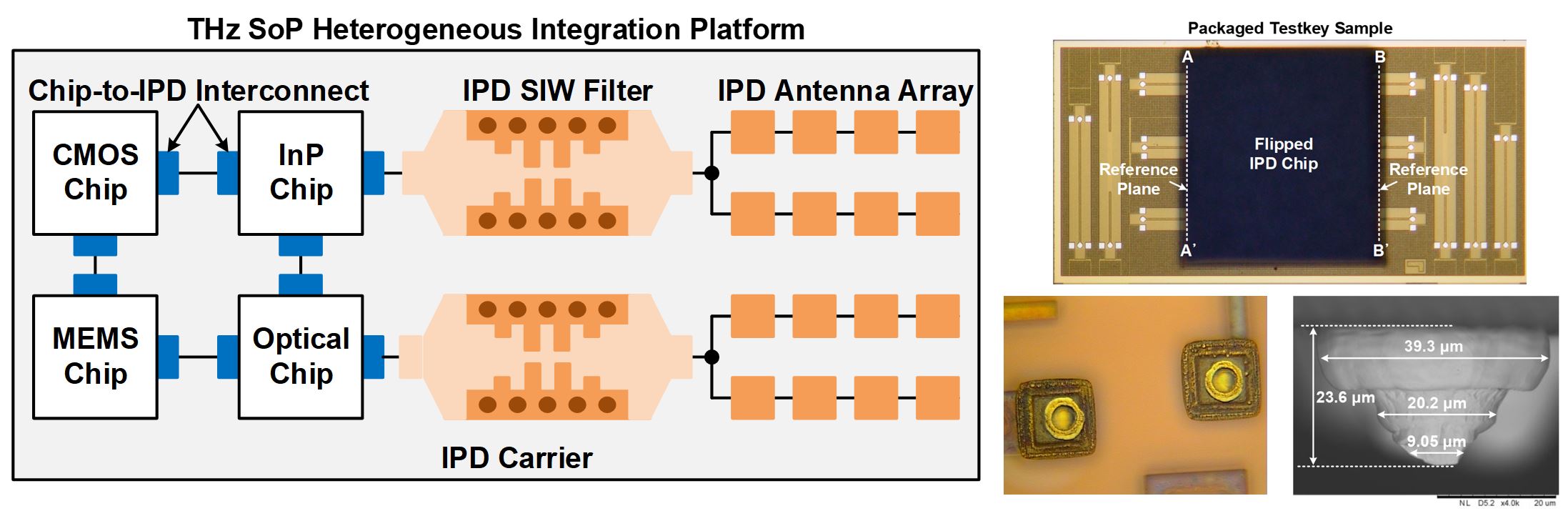

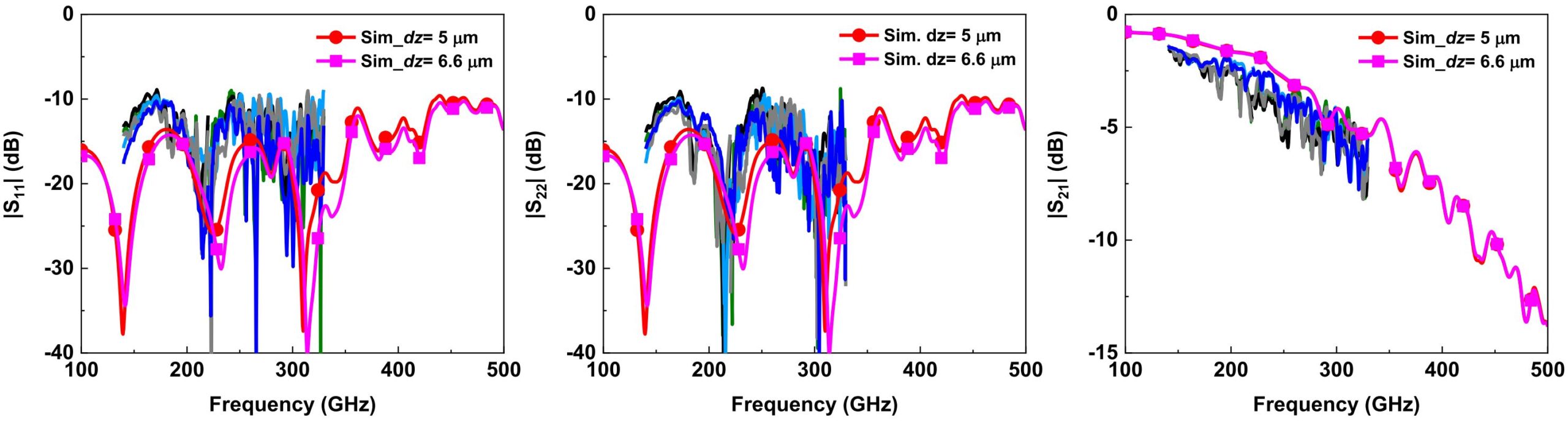

A system-on-a-chip (SoC) integration approach using CMOS technologies, that is, all the active and passive components are integrated into a single CMOS chip, is often adopted to realize THz systems for the aforementioned applications. However, THz SoC system design using CMOS technologies is challenging due to low supply voltages, limited transistor speeds, lossy silicon substrates, and unfavorable back end of lines (BEOL), inevitably resulting in passive components with low-quality factors (Q), low-maximum-oscillation-frequency (fmax) transistors, and low-gain on-chip antennas. A system-on-package (SoP) integration approach is a promising alternative to solve the aforementioned CMOS SoC design issues. Building blocks of a THz system implemented in different favorable technologies, respectively, are integrated onto a common low-loss and low-cost carrier. Hence, the unique advantages of these different technologies, e.g., fmax > 1 THz transistors provided by InP HBT technologies, high-speed digital-signal-processing (DSP) capability by CMOS chips, and high-gain on-carrier antenna arrays offered by IPD carriers can be utilized to carry out low-power, compact, high-performance, and high-integration THz systems. Even the optical components can also be integrated with electronic chips on the same carrier to realize a high-performance hybrid electronic-photonic system. Obviously, to make the SoP heterogeneous system integration feasible, a low-loss THz interconnect for transiting a signal from a chip to a carrier is a must. We are investigating novel mm-Wave and THz packaging techniques to enable the THz SoP heterogeneous system integration. We have successfully realized low-loss and broadband CMOS (0.18-μm CMOS, 90-nm CMOS, and 40-nm CMOS) to IPD (Glass IPD, high-Z-Si IPD, and GaAs IPD) interconnects working up to 500 GHz using gold-stud bumps and bondwires. (Selected publication TTST’22, TMTT’19, TMTT’15, TMTT’13)

♦ RF, mm-Wave, and THz IC designs

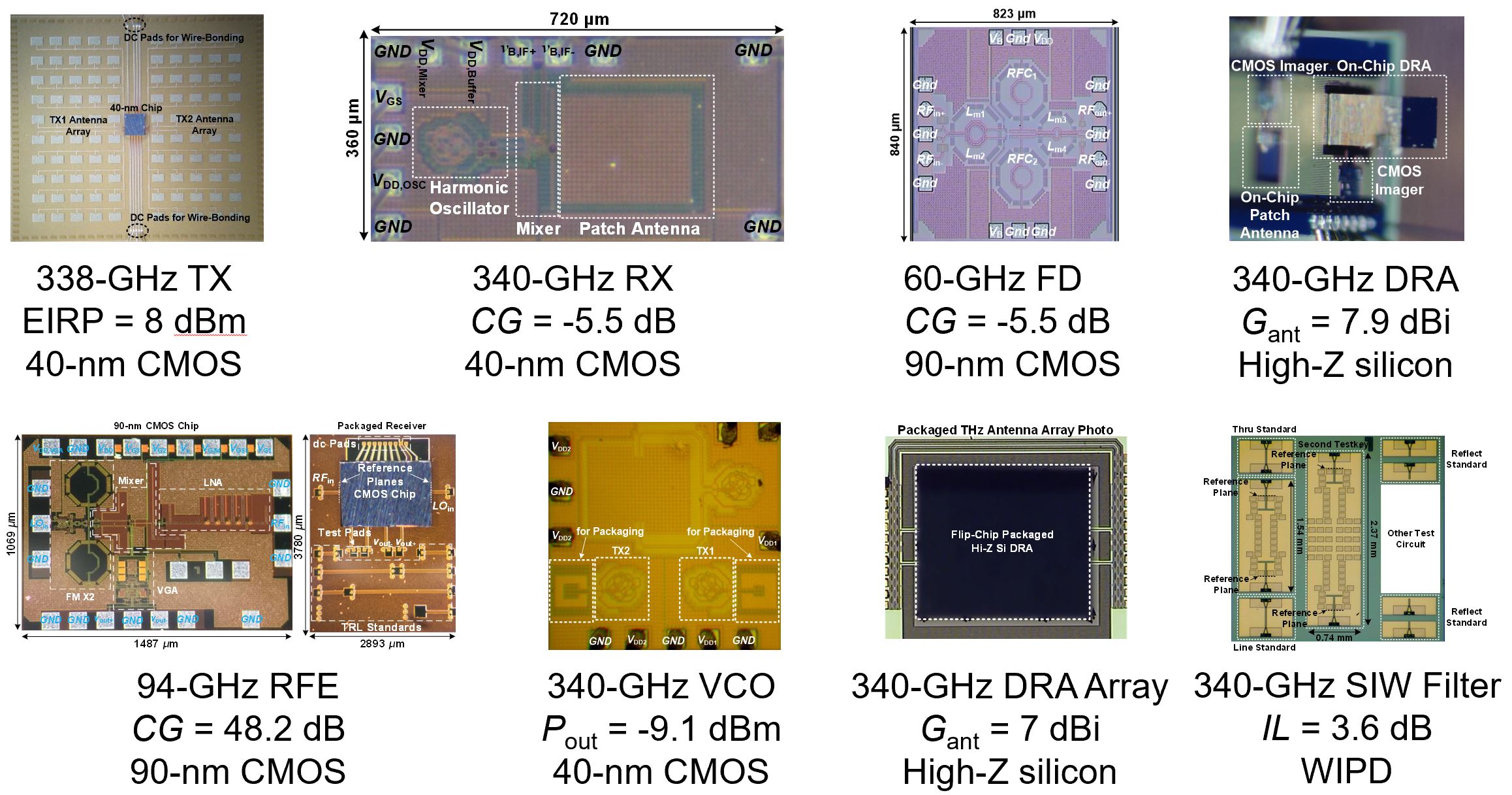

Due to the limited transistor speed, low supply voltage, and unfriendly back-end of lines existing in CMOS technologies, new circuit topologies and design techniques must be developed in order to extend the operation frequencies of electronic circuits up to THz frequencies with excellent performance. We investigate novel circuit architectures, reciprocal-embedding techniques, broadband and high-efficiency antennas, antenna-in-package (AiP) techniques, and low-loss transmission lines at 140-GHz, 240-GHz, and 340-GHz bands for THz imaging and radar applications. We have successfully realized

(i) Active circuits, including 28-GHz 10-bit 360-degree CMOS phase shifter, 22-33-GHz mixer with configurable bondwire resonators, reconfigurable 35-GHz CMOS receiver supporting active and passive detections, 60-GHz balun-less frequency doubler with differential output, 94-GHz W-band flip-chip-assembly CMOS receiver, 340-GHz voltage-controlled oscillator with differential output, 340-GHz SoP-based THz transmitter with 50 on-carrier antennas integrated, 340-GHz heterodyne CMOS receiver, and 340-GHz THz imager with 256 antennas integrated. (TVLSI’17, Access’21, TVLSI’18, TMTT’19, MWCL’14, TMTT’15, TTST’16, Access’19)

(ii) Passive circuits, including 340-GHz higher-order-mode dielectric resonator antennas (DRA), DRA array, 340-GHz substrate-integrated waveguide (SIW), and 340-GHz Chebyshev SIW filter. (Access’21, Access’19, TTST’17)

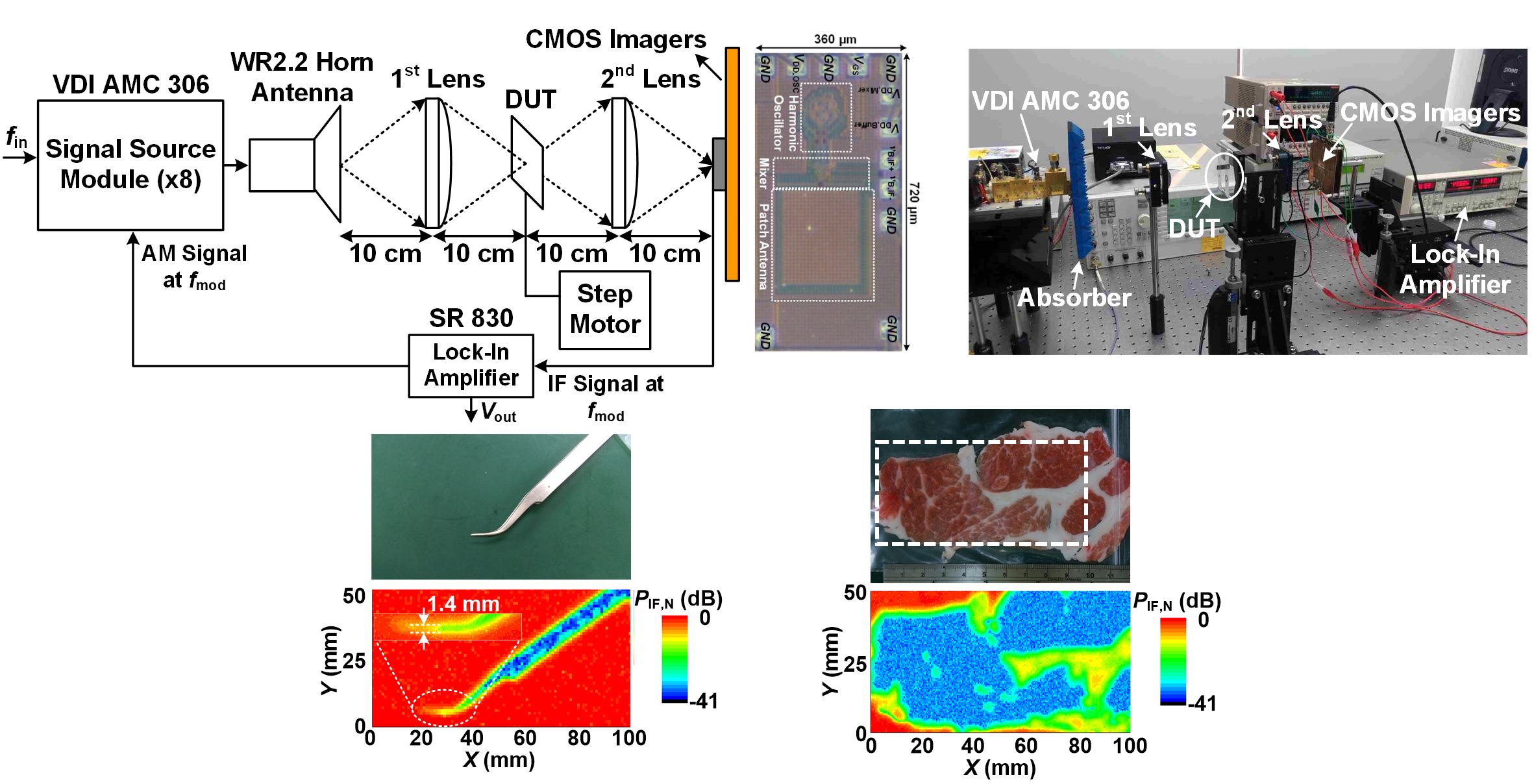

♦ THz imaging systems

We use our designed 340-GHz THz CMOS RFE with commercial VDI components to set up a transmissive THz imaging system. To test the spatial resolution of the established THz imaging system, the first DUT is selected as a tweezer. From the taken image, the resolution can be estimated to be 1.4 mm, close to the theoretical value of 1.1 mm according to the Rayleigh criterion. Another DUT chosen is a thin layer of pork with a thickness of around 1 mm. The taken image illustrates that the THz signal can penetrate through the fat, but not the lean meat and muscle. This is due to the fact that muscle and meat contain more water than fat. We are investigating novel image architectures to realize a real-time THz imaging system. (TTST’16)

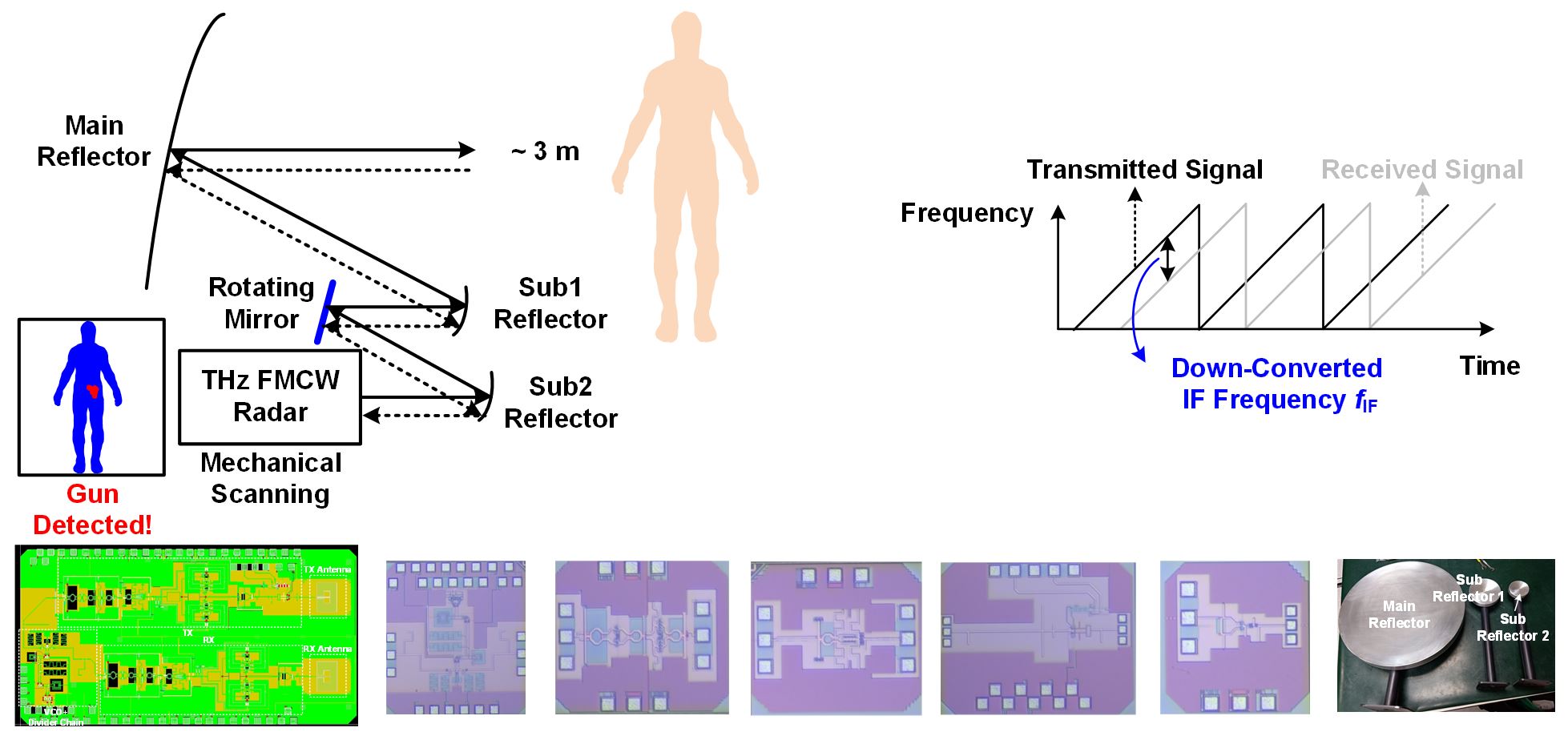

♦ THz FMCW radar systems

THz FMCW radars can be employed to realize reflective-type THz imaging systems for security applications in public places. Moreover, the operation distance can greatly extend as reflector antennas are integrated. So far we are investigating novel system architectures to realize a 340-GHz FMCW radar for real-time security applications. Many critical circuit blocks and reflector antennas of the THz FMCW radar systems have been designed and verified.

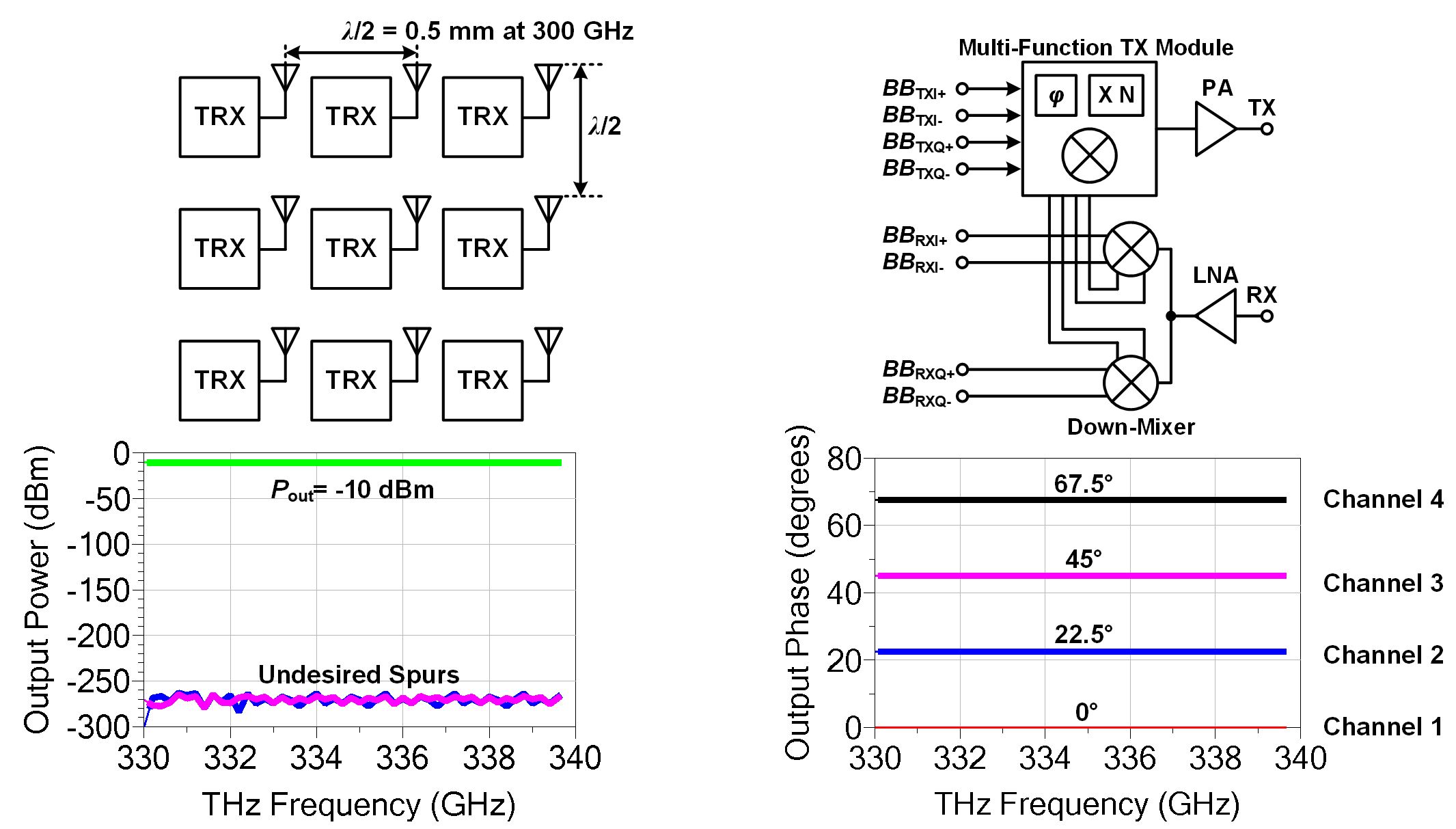

♦ sub-THz/THz Communication Systems

Phased-array techniques are critical for mm-Wave, sub-THz, and THz wireless systems to tackle the issue of high path loss. We are investigating novel phased-array architectures for sub-THz/THz 6G communication applications. So far we have invented new phased-array architectures suitable for working at sub-THz/THz frequencies. US and RoC patents are filed and pending. We are designing phased-array THz transceivers at 140-GHz, 240-GHz, and 340-GHz bands using the proposed novel scalable phased-array architectures.

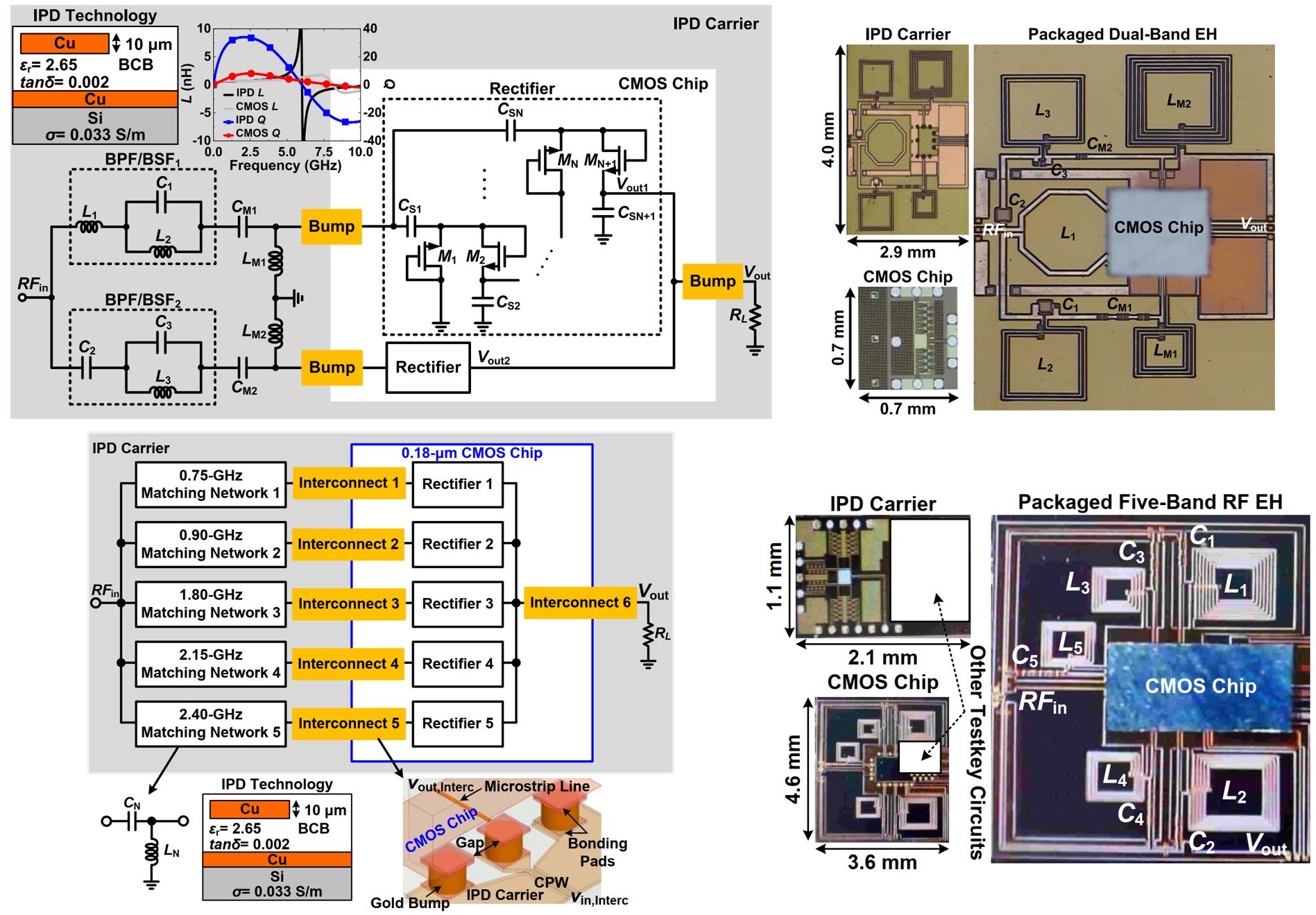

♦ High-efficiency multi-band RF and mm-Wave energy harvesters

RF energy harvesters are critical components for self-sustainable IoT devices. We have successfully realized dual-band and penta-band RF energy harvesters using an SiP technique. We are investigating novel harvester architectures and optimization techniques to harvest more frequency bands and extend the operation frequencies up to mm-Wave bands. (MWCL’17, RWS’18)